#### Continuous-time Digital Signal Processing for Audio Feature Extraction integrated in 28nm FD-SOI CMOS

#### Antoine Frappé, Benoit Larras, Angel Gonzalez, Andreas Kaiser, Philippe Cathelin

**November 8 2017**

## Outline

- I. Context : Voice Activity Detection

- II. State-of-the-art

- III. Proposed concepts Opportunities and challenges

## Outline

- Context

- I. Context : Voice Activity Detection

- II. State-of-the-art

- III. Proposed concepts Opportunities and challenges

## Ambient Intelligence / IoT

- Massive amounts of data

- Always-on sensing

Context

#### To process locally OR to transfer to main computation unit (cloud)

#### ENERGY HUNGRY

4

## Ambient Intelligence / IoT

- Massive amounts of data

- Always-on sensing

Context

je, de Microélectronique et de Nanotechnologi

#### To process locally OR to transfer to main computation unit (cloud)

#### ENERGY HUNGRY

Small, cheap, no battery replacement **→ Towards Near-Sensor Computing**

5

## Applications

Audio processing

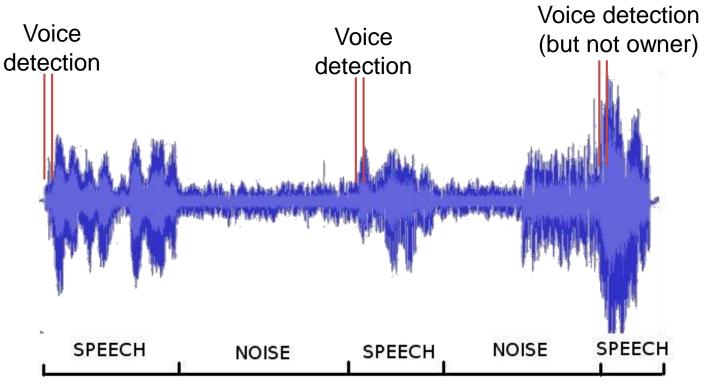

- Voice Activity Detection in noisy context

- Vowels, words, language recognition

- Specific feature extraction

- Human-body signal classifications

ECG, EEG, etc...

- Vibration monitoring

- Image processing

- Motion-triggered cameras

- Face detection / Owner-activated devices

#### Focus on audio processing

• Example : Voice activity detection

#### In the presence of noise

• Triggered device is almost always ON !

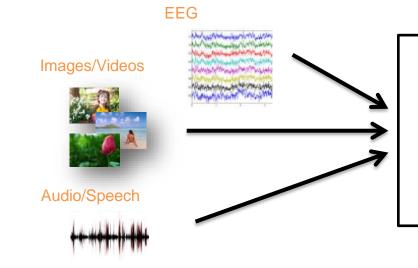

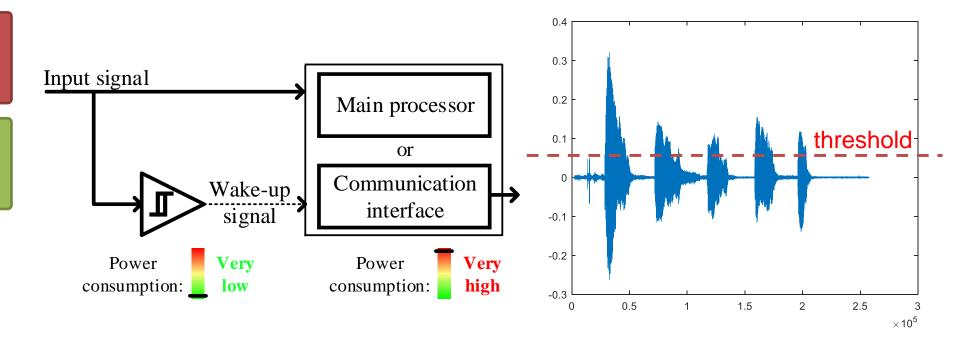

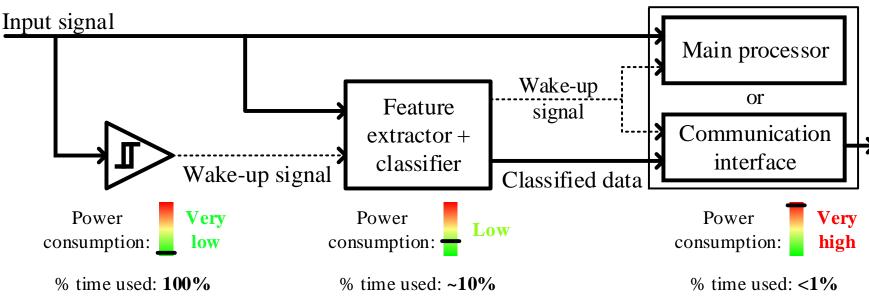

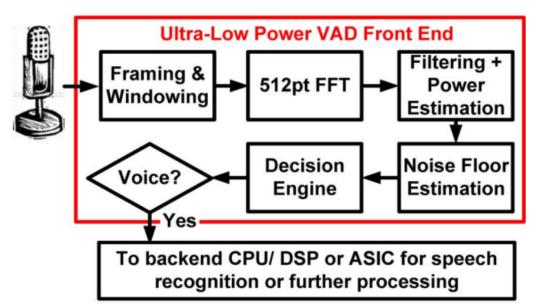

## **Voice Activity Detection**

« Wake-on-feature »

#### Embedded processing chain

## Outline

- I. Context : Voice Activity Detection

- II. State-of-the-art

- III. Proposed concepts Opportunities and challenges

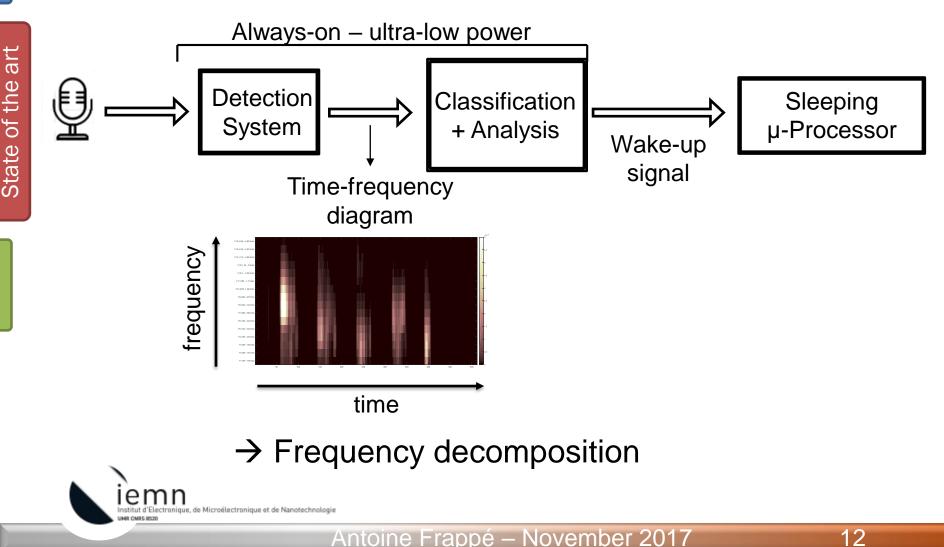

### VAD State-of-the art

## Fully digital implementation

[Raychowdhury JSSC Aug 2013]

Georgia Tech / Intel

- ++ Fully configurable / Highly integrated

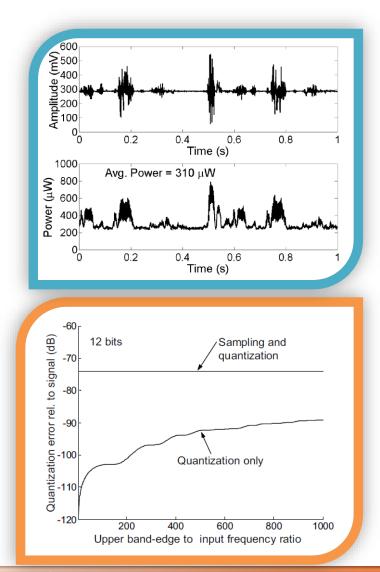

- High sample rate (~10MHz) →

energy consumption is high VAD >100µW (without ADC)

State of the art

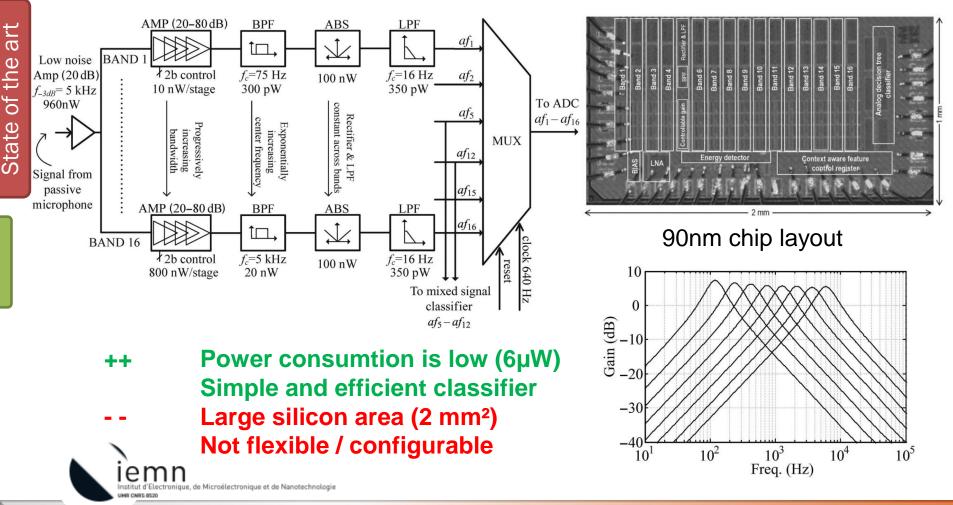

### Fully analog implementation

[Badami JSSC Jan 2016]

**KU** Leuven

Antoine Frappé – November 2017

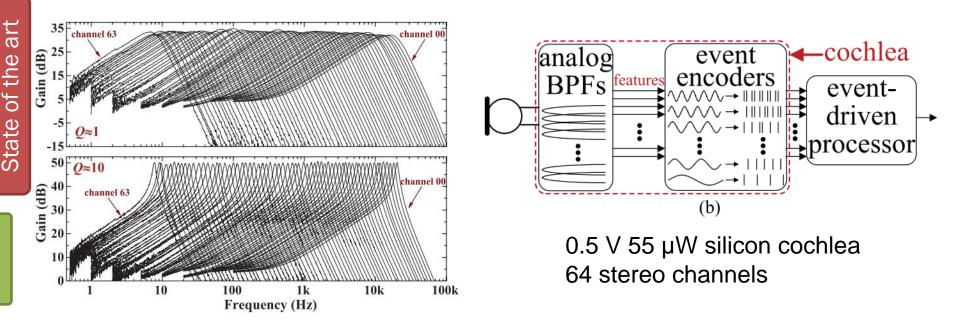

#### Analog filter banks + event encoders

[Yang JSSC Nov 2016] ETH Zurich

++ Enhanced feature resolution

Bioinspired from human cochlea

- Large silicon area (> 50 mm<sup>2</sup> in 0.18µm CMOS)

## Outline

- I. Context : Voice Activity Detection

- II. State-of-the-art

- III. Proposed concepts Opportunities and challenges

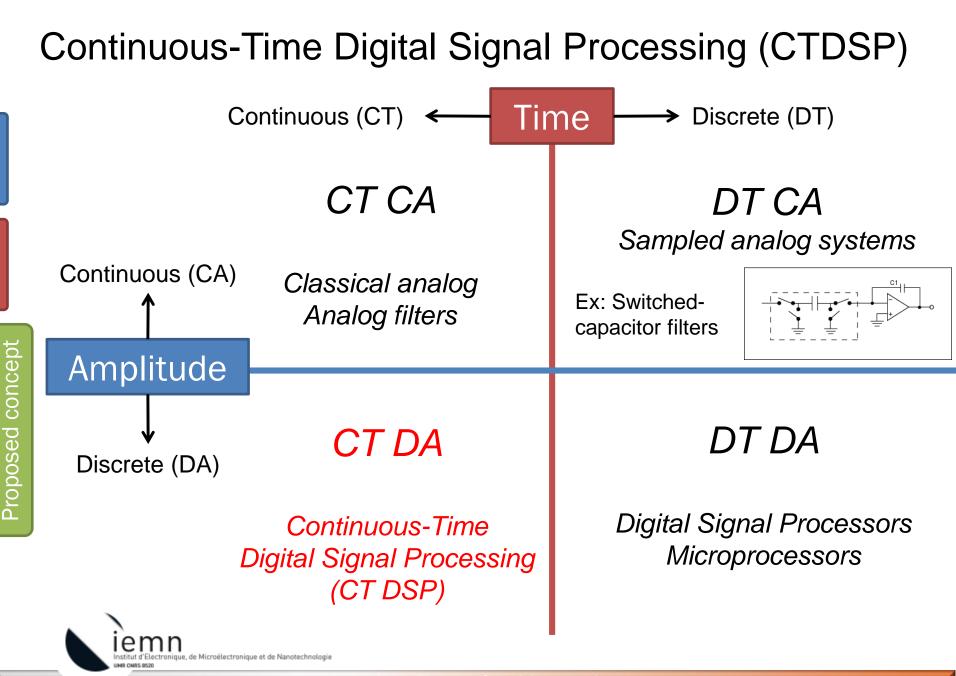

- I. Continuous-time DSP

- II. Associative memories

#### **Proposed concept**

Exploring innovative circuit structures in fine-pitch CMOS technologies

#### **CT DSP Opportunities**

#### CMOS Digital System Configurability Scalability High integration level

#### Event-driven system No clock Event-driven power consumption

#### Quantization-first No aliasing Reduced ADC resolution

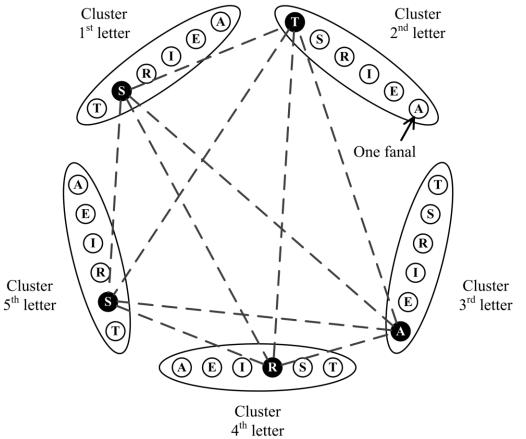

#### Integrated associative memories

• Example : Clustered clique-based networks

concept

Proposed

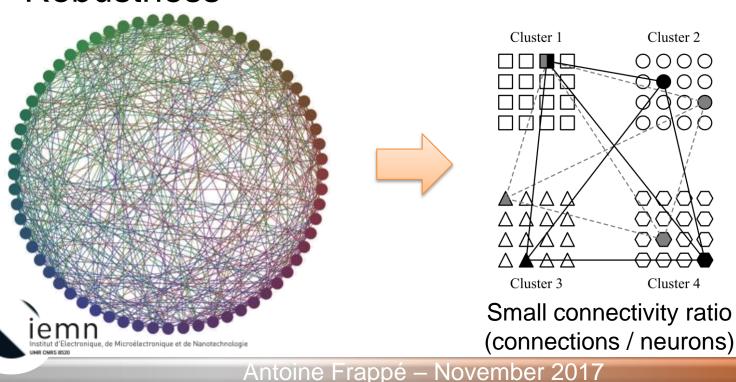

#### Integrated associative memories Opportunities

- Suitable for small classification tasks

- Low-energy / application specific

- Robustness

concept

Proposed

## Challenges

- CT DSP

- Event-driven processing with no clocks is difficult to handle and design (concepts, tools)

- Timing is critical...

- Associative memories

- Generic topology vs. diversity of applications

- Bridging the gap from theory to efficient hardware

- Latency !

Proposed concept

Integration in advanced CMOS technology

### Conclusion

- Proposed radical change in concepts to implement ultra-low power feature extraction and classification

- Best of both analog and digital worlds

- Demonstration on audio processing

- CT DSP

- Associative memories

- Objective : demonstration of a « wake-on feature » highly-efficient embedded system in 28nm FDSOI CMOS

# We are open to any suggestions, questions, collaborations, discussions,...

#### antoine.frappe@yncrea.fr Silicon Microelectronics Group

24